上图是镁光 NAND FLASH MT29F1G08ABAEAH4的引脚(Pin)所对应的功能,简单翻译如下:

1. I/O0 ~ I/O7:用于输入地址/数据/命令,输出数据

2. CLE:Command Latch Enable,命令锁存使能,在输入命令之前,要先在模式寄存器中,设置CLE使能

3. ALE:Address Latch Enable,地址锁存使能,在输入地址之前,要先在模式寄存器中,设置ALE使能

4. CE#:Chip Enable,芯片使能,在操作Nand Flash之前,要先选中此芯片,才能操作

5. RE#:Read Enable,读使能,在读取数据之前,要先使CE#有效。

6. WE#:Write Enable,写使能,在写取数据之前,要先使WE#有效。

7. WP#:Write Protect,写保护

8. R/B#:Ready/Busy Output,就绪/忙,主要用于在发送完编程/擦除命令后,检测这些操作是否完成,忙,表示编程/擦除操作仍在进行中,就绪表示操作完成.

9. Vcc:Power,电源

10. Vss:Ground,接地

11. N.C:Non-Connection,未定义,未连接。

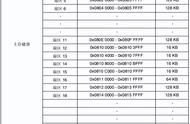

实际项目的NAND FLASH原理图

上图中我们可以发现有两个地方需要上拉电阻R/B#:、WP#,其他都是CPU同nand flash直接相连接。通过查询flash 的datasheet可以发现,这两个引脚是开漏极输出,需要上拉电阻。

而且可以看到电路设计中WP#引脚一端接上拉电阻,一端通过二极管和0欧姆电阻连接到CPU复位引脚,CPU主芯片平台的复位是低电平复位,WP#引脚是低电平的时候写保护有效,这样做的目的就是,在复位期间,即CPU复位引脚为低电平期间此时WP#引脚也为二极管电压(0.7V)为低电平,为写保护状态,在复位期间,CPU引脚状态不定,容易对flash进行误操作。这样做的目的就是硬件实现在CPU复位期间,flash是写保护状态,不允许写入的。

很多时候掉电产生的擦除数据,导致数据丢失无法开机、无法保存掉电记忆等等问题都可以使用这个方案来对策解决问题。

为何需要ALE和CLE

比如命令锁存使能(Command Latch Enable,CLE)和地址锁存使能(Address Latch Enable,ALE),那是因为,Nand Flash就8个I/O,而且是复用的,也就是,可以传数据,也可以传地址,也可以传命令,为了区分你当前传入的到底是啥,所以,先要用发一个CLE(或ALE)命令,告诉nand Flash的控制器一声,我下面要传的是命令(或地址),这样,里面才能根据传入的内容,进行对应的动作。否则,nand flash内部,怎么知道你传入的是数据,还是地址,还是命令啊,也就无法实现正确的操作了。

Nand Flash只有8个I/O引脚的好处

1. 减少外围引脚:相对于并口(Parellel)的Nor Flash的48或52个引脚来说,的确是大大减小了引脚数目,这样封装后的芯片体积,就小很多。现在芯片在向体积更小,功能更强,功耗更低发展,减小芯片体积,就是很大的优势。同时,减少芯片接口,也意味着使用此芯片的相关的外围电路会更简化,避免了繁琐的硬件连线。

2. 提高系统的可扩展性,因为没有像其他设备一样用物理大小对应的完全数目的addr引脚,在芯片内部换了芯片的大小等的改动,对于用全部的地址addr的引脚,那么就会引起这些引脚数目的增加,比如容量扩大一倍,地址空间/寻址空间扩大一倍,所以,地址线数目/addr引脚数目,就要多加一个,而对于统一用8个I/O的引脚的Nand Flash,由于对外提供的都是统一的8个引脚,内部的芯片大小的变化或者其他的变化,对于外部使用者(比如编写nand flash驱动的人)来说,不需要关心,只是保证新的芯片,还是遵循同样的接口,同样的时序,同样的命令,就可以了。这样就提高了系统的扩展性。

片选无关(CE don’t-care)技术