端为1,加到场效应管栅极的信号为1,该场效应管就导通,对地呈现低阻抗,此时即使引脚上输入的信号为1,也会因端口的低阻抗而使信号变低,使得外加的1信号读入后不一定是1,若先执行置1操作,则可以使场效应管截止,引脚信号直接加到三态缓冲器中,实现正确的读入,由于在输入操作时还必须附加一个准备动作,所以这类I/O口被称为准双向口,89C51的P0、P1、P2、P3口作为输入时都是准双向口。接下来再看另一个问题,从图1-10中可以看出,这4个端口还有一个差别,除了P1口外,P0、P2、P3口都还有其他功能,这些功能又作什么用的呢?下面就来详细讲解这个问题。

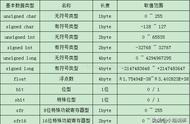

每个I/O端口都有一个8位数据锁存器和两个8位数据缓冲器。P0~P3(8位锁存器)是SFR,有各自的端口地址,可直接用指令寻址,用于存放需要输出的数据。数据输入时只有缓冲没有锁存,各引脚上输入的数据必须一直保持到CPU将其读走为止,如图1-11所示为P0位结构图。

图1-11 P0位结构图

从图1-11中可以看出,P0口的内部有一个二选一的选择器,受内部信号的控制,如果在图1-11中的位置,则处在I/O口工作方式,此时相当于一个准双向口输入,须先将P0口置1,每根口线可以独立定义为输入或输出,但是必须在口线上加上拉电阻,如果将开关拨向另一个方向,则作为地址/数据复用总线用,此时不能逐位定义为输入/输出,有两种用法,当作数据总线用时输入8位数据,当作地址总线用时则输出低8位地址,注意,当P0口作为地址/数据复用总线用之后就不能再作I/O口使用了。那么什么叫做地址/数据复用?这其实是当单片机的并行口不够用时需要扩展输入/输出口时的一种用法,具体使用方法会在后续的章节中逐步讲解。

利用P0口进行扩展外部存储器和I/O时,P0口将作为地址和数据分时复用,CPU发控制信号,打开与门,使MUX打向上边,形成推拉式结构,数据信号可直接读入或输出到内部总线。利用P0作为通用I/O时,此时P0口是一个准双向口,CPU发控制信号,封锁与门,使上拉管截止,MUX打向下边,与D触发器Q连接。

输入程序举例:

MOV P0, #FFH

输出程序举例:

MOV A, P0

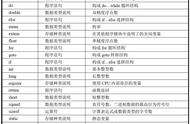

2. P1口的结构及工作原理

P1口字节地址为90H,位地址为90H~97H,如图1-12所示为P1位结构图。

图1-12 P1位结构图

与P0不同,P1口只能作为I/O口使用,无MUX,但其内部有一个上拉电阻,所以连接外围负载时不需要外接上拉电阻,这一点P1、P2、P3都一样。

输入程序举例:

MOV P1, #FFH

MOV A, P1

输出程序举例:

MOV A, P1

3. P2口的结构及工作原理

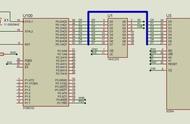

P2口字节地址为A0H,位地址为A0H~A7H,如图1-13所示为P2位结构图。

图1-13 P2位结构图

P2口作为I/O口线时用法与P0口一样,当内部开关拨向另一个方向,即作地址输出时,可以输出程序存储器或外部数据存储器的高8位地址,并与P0口输出的低地址一起构成16位的地址线。

注意: 和数据总线的区别,数据总线是8位的,很多书上都会提到51单片机是8位数据总线,16位地址总线,但都不会解释有什么不同,看到这里读者应该明白二者的区别。

16位的地址总线可以寻址64KB的程序存储器或外部数据存储器,后续章节会讲解,此处要注意的是当P2口作为地址总线时,高8位地址线是8位一起输出的,不能像I/O口线那样逐位定义,这与P0口是一样的。

当P2口用来扩展外存储器和I/O时,作为高8位地址输出,当进行外部存储器或I/O设备读写操作时,CPU自动发出控制信号,打开与门,使MUX拨向上边。当P2口当作通用I/O时,CPU自动发出控制信号,MUX拨向下边,与D触发器Q连接。

输入程序举例:

MOV P2, #FFH

MOV A, P2

输出程序举例:

MOV A, P2

4. P3口的结构及工作原理

P3口字节地址为B0H,位地址为B0H~B7H。如图1-14所示为P3位结构图。