NVM Express(NVMe),或称非易失性内存主机控制器接口规范(英语:Non Volatile Memory Host controller Interface Specification,缩写:NVMHCIS),是一个逻辑设备接口规范。它是与AHCI类似的、基于设备逻辑接口的总线传输协议规范(相当于通讯协议中的应用层),用于访问通过PCI Express(PCIe)总线附加的非易失性存储器介质(例如采用闪存的固态硬盘驱动器),虽然理论上不一定要求 PCIe 总线协议。

1. 综述

NVMe over PCIe协议,定义了NVMe协议的使用范围、指令集、寄存器配置规范等。

1.1 名词解释

1.1.1 NamespaceNamespace是一定数量逻辑块(LB)的集合,属性在Identify Controller中的数据结构中定义。

1.1.2 Fused OperationsFused Operations可以理解为聚合操作,只能聚合两条命令,并且这两条命令在队列中应保持相邻顺序。协议中只有NVM指令才有聚合操作。还需要保证聚合操作的两条命令读写的原子性,参考Compare and Write例子。

1.1.3 指令执行顺序除了聚合操作(Fused Operations),每一条SQ中的命令都是独立的,不必考虑RAW等数据相关问题,即使考虑,也是host应该解决的问题。

1.1.4 写单元的原子性控制器需要支持写单元的原子性。但有时也能通过host配置Write Atomicity feature,减小原子性单元的大小,提高性能。

1.1.5 元数据数据的额外信息,相当于提供校验功能。可选的方式。

1.1.6 仲裁机制用来选择下一次执行的命令的SQ的机制,三种仲裁方式:

- RR(每个队列优先级相同,轮转调度)

- 带权重的RR(队列有4种优先级,根据优先级调度)

- 自定义实现

NVMe定义的最小的读写单元,2KB、4KB……,用LBA来标识块地址,LBA range则表示物理上连续的逻辑块集合。

1.1.8 Queue Pair由SQ(提交队列)与CQ(完成队列)组成,host通过SQ提交命令,NVMe Controller通过CQ提交完成命令。

1.1.9 NVM 子系统NVM子系统包括控制器、NVM存储介质以及控制器与NVM之间的接口。

1.2 NVMe SSD1.2.1基本架构整体来看,NVMe SSD可以分为三部分,host端的驱动(NVMe官网以及linux、Windows已经集成了相应的驱动)、PCIe NVMe实现的控制器以及FTL NAND Flash的存储介质。

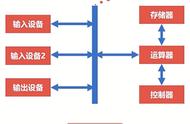

NVMe控制器实质上为DMA multi Queue,DMA负责数据搬运(指令 用户数据),多队列负责发挥闪存的并行能力。

NVMe over PCIe,通过利用PCIe总线实现数据交互的功能,实现对物理层的抽象功能。

2.1 PCIe总线的基本结构PCIe总线分为三层,物理层,数据链路层,处理层(类似于计算机网络的分层结构),通过包来转发数据。NVMe协议定义的内容相当于PCIe的上一层应用层,处于应用层。PCIe给NVMe提供了底层的抽象。

NVMe SSD相当于一个PCIe的端设备(EP)。

在协议中主要定义了PC header、PCI Capabilities和PCI Express Extended Capabilities三部分内容。

具体在host内存中会占有4KB,结构如下: