两个OC电路实现“线与”

(4)总线的I/O接口上下拉电阻。

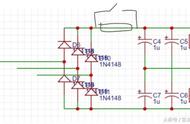

一些总线有输出输出接口,本质就是OC或OD的接口。I2C(Inter Integrated Circuit,内部集成电路)总线就是典型的OD输出结构的应用,典型的I2C电路都有上拉电阻,如图所示。

I2C总线上拉电阻

I2C接口的SCL与SDA都是OD输出结构输出,这样的好处是可以作为双向数据总线。OC、OD电路往往是刚刚说的输入输出管脚,然而一些总线的I/O就是一些双向数据的信号,其实就是把输入和输出短接在一起,然后把输出做成OC或OD。这样处理不单用一根信号实现了双向数据,既可以输出又可以输入,同时解决了双向数据如果同时发送带来的数据冲突的问题。

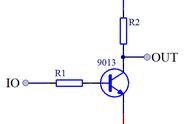

一般来说,芯片的输出管脚是推挽结构。如果两个芯片的推挽结构输出管脚连接在一起,某一个时刻两个芯片同为输出,一个如果输出为高、一个输出为低,则可能出现短路的现象,工作中称为“总线冲突”,如图所示。用OC、OD电路可以避免短路,所有绝大多数总线都是采用这种方式设计,如I2C、LPC、PCI等总线的输入输出管脚都是这样的管脚类型。当然也有些总线方式,I/O端口不需要外接,是芯片内置了上拉电阻。

推挽结构输出管脚短路

对于I2C总线,总线上有两个芯片或多个芯片,所有芯片的引脚输出什么状态,都不会出现短路的情况引起数据冲突,配合各自芯片内部的数据识别电路及仲裁系统,双方都可以主动给另一方发送信息。也就是说,任何一方都可以将拉低,不拉低时就是释放总线,总线上为高电平,而不会影响起数据冲突,如图31.10所示。

OC输出管脚电流

(5)增加输出管脚的驱动能力。

芯片的输出管脚本身并不是OC、OD,但是有时我们也会增加一个上拉电阻或下拉电阻,通过上拉或下拉来增加或减小驱动电流。

例如,一个单片机的I/O口内部有一个几十kΩ,最大输出电流也就是250μA,因此当我们增加一个上拉电阻时,可以形成和内部上拉电阻并联结构,增加高电平时电流的输出能力。在负载增大时,仍然能够保持足够的电压。

(6)电平标准匹配。

改变电平的电位,常用在TTL-CMOS匹配。当TTL电路驱动COMS电路时,若TTL电路输出的高电平低于COMS电路的最低高电平(一般为3.5V),这时就需要在TTL的输出端接上拉电阻,以提高输出高电平值。需要注意的是,此时上拉电阻连接的电压值应不低于CMOS电路的最低高电压,同时又要考虑TTL电路方的电流(如某端口最大输入或输出电流)的影响。

(7)增强电路抗干扰能力。

芯片的管脚加上拉电阻来提高输出电平,从而提高芯片输入信号的噪声容限,增强抗干扰能力。长线传输中,电阻不匹配容易引起反射波干扰,加上下拉电阻是电阻匹配,有效地抑制反射波干扰。提高总线的抗电磁干扰能力,管脚悬空就比较容易受外界的电磁干扰。

3)上拉电阻阻值选择原则

(1)从节约功耗及芯片的灌电流能力考虑,电阻值应当足够大;电阻越大,电流越小。

(2)从确保足够的驱动电流考虑,电阻值需要足够小;电阻越小,电流越大。

(3)对于高速电路,过大的上拉电阻可能边沿变平缓。需要电阻与电路寄生电容形成RC滤波电路,影响信号的高频分量的传输。

(4)驱动能力与功耗的平衡。以上拉电阻为例,一般地说,上拉电阻越小,驱动能力越强,但功耗越大,设计时应注意两者之间的均衡。

(5)下级电路的驱动需求。同样以上拉电阻为例,当输出高电平时,开关管断开,上拉电阻应适当选择以能够向下级电路提供足够的电流。

(6)高低电平的设定。不同电路的高低电平的门槛电平会有不同,电阻应适当设定以确保能输出正确的电平。以上拉电阻为例,当输出低电平时,开关管导通,上拉电阻和开关管导通电阻分压值应确保在零电平门槛之下。

(7)频率特性。以上拉电阻为例,上拉电阻和开关管漏源级之间的电容和下级电路之间的输入电容会形成RC延迟,电阻越大,延迟越大。上拉电阻的设定应考虑电路在这方面的需求。

4)吸电流、拉电流、灌电流

在集成电路中,吸电流、拉电流输出和灌电流输出是一个很重要的概念。

拉电流:主动输出电流,是从输出口输出电流。

灌电流:被动输入电流,是从输出端口流入吸电流。

吸电流:吸则是主动吸入电流,是从输入端口流入吸电流和灌电流就是从芯片外电路通过引脚流入芯片内的电流,区别在于吸收电流是主动的,从芯片输入端流入的叫吸收电流。

拉电流是数字电路输出高电平给负载提供的输出电流,灌电流时输出低电平是外部给数字电路的输入电流,它们实际就是输入、输出电流能力。

吸电流是对输入端(输入端吸入)而言的;而拉电流(输出端流出)和灌电流(输出端被灌入)是相对输出端而言的。

,