UART——通用异步收发传输器,UART 作为异步串口通信协议的一种,工作原理是将传输数据的每个字符一位接一位地传输。在应用程序开发过程中使用频率较高的数据总线。基于UART的数据传输是异步形式的串行数据传输。基于UART的串行数据传输不需要使用时钟信号来同步传输的发送端和接收端,而是依赖于发送设备和接收设备之间预定义的配置。对于发送设备和接收设备来说,两者的串行通信配置(波特率、单位字的位数、奇偶校验、起始位数与结束位、流量控制)应该设置为完全相同。通过在数据流中插入特定的比特序列,可以指示通信的开始与结束。当发送一个字节数据的时候,需要在比特流的开头加上起始位,并在比特流的末尾加上结束位。数据字节的最低位紧接在起始位之后。UART 串口的特点是将数据一位一位地顺序传送,只要2 根传输线就可以实现双向通信,一根线发送数据的同时用另一根线接收数据。UART 串口通信有几个重要的参数,分别是波特率、起始位、数据位、停止位和奇偶检验位,对于两个使用UART 串口通信的端口,这些参数必须匹配,否则通

- 起始位:表示数据传输的开始,电平逻辑为“0” 。

- 数据位:可能值有5、6、7、8、9,表示传输这几个bit 位数据。一般取值为8,因为一个ASCII 字符值为8 位。

- 奇偶校验位:用于接收方对接收到的数据进行校验,校验“1” 的位数为偶数(偶校验) 或奇数(奇校验),以此来校验数据传送的正确性,使用时不需要此位也可以。

- 停止位:表示一帧数据的结束。电平逻辑为“1”。

- 波特率:串口通信时的速率,它用单位时间内传输的二进制代码的有效位(bit) 数来表示,其单位为每秒比特数bit/s(bps)。常见的波特率值有4800、9600、14400、38400、115200 等,数值越大数据传输的越快,波特率为115200 表示每秒钟传输115200 位数据。

1-Wire接口是由Maxim Dallas半导体公司(首页为http://www.maxim-ic.com)开发的异步半双工通信协议,也称为Dallas 1-Wire®协议。其中,按照主-从通信模型,只使用单条信号线DQ实现通信。1-Wire总线的一个重要特征在于,该总线允许在信号线上传输能量。1-Wire接口支持在总线上连接单个主设备以及一个或多个从设备。

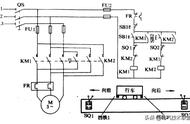

板上并行接口(parallel interface)通常用于系统与外围设备之间的通信,其中,外围设备通过存储器映射到系统的主控端。只要嵌入式系统的主控处理器/控制器含有并行总线,支持并行总线的设备就可以直接连接到该总线系统上。外围设备与主控端之间具有控制信号接口,可以控制并行总线上的数据通信。这里,通信的控制信号包括读/写信号和设备选择信号。一般说来,外围设备具有设备选择线;只有当主控处理器选通该线的时候,该设备才是有效的。数据传输的方向可以是从主控端到外围设备,也可以是从外围设备到主控端;这是通过读和写控制信号线进行控制的。只有主控处理器能够控制读控制信号和写控制信号。一般说来,外围设备通过存储器映射到主控处理器,从而可以访问分配的地址范围。此时,设备需要使用地址译码电路来产生芯片选择信号。当处理器选择的地址位于设备指定范围内的时候,译码电路对芯片选择线进行触发,从而激活设备。然后,处理器可以使能相应的控制线(分别是RD\与WD\),从而由设备读出数据,或者是向设备写入数据。为了实现并行通信,系统需要严格遵循时序规范。前面已经提到过,并行通信是由主控处理器启动的。如果某外围设备想要对通信进行初始化,那么可以向处理器发出中断,告知相关信息。为了实现上述功能,设备的中断线需要连接到处理器的中断线上,并且主控处理器需要触发相应的中断。需要说明的是,主控处理器的数据总线宽度决定了并行接口的宽度,可以是4位、8位、16位、32位、64位等。设备支持的总线宽度应该与主控处理器完全相同。

免责声明:本文内容来源于网络,整理者李逍遥;文章版权归原作者所有,意在传播相关技术知识&行业趋势,供大家学习交流,若涉及作品版权问题,请联系删除或授权事宜。