图2-2 80C51/80C52的引脚分布与封装图

1.电源及时钟信号引脚

Vcc:正常工作或对内部EPROM烧写程序时,接 5V电源。

GND:地。

XTAL1:时钟信号输入引脚,内部振荡电路的输入端。

X...

2.输入/输出引脚

MCS-51单片机有4组8位I/O端口:P0、P1、P2和P3端口,P1、P2和P3为准双向端口,P0端口则为双向三态输入/输出端口。在DIP封装中,引脚39~32为P0.0~P0.7输入/输出引脚,引脚1~8为P1.0~P1.7输入/输出引脚,引脚21~28为P2.0~P2.7输入/输出引脚,引脚10~17为P3.0~P3.7输入/输出引脚。

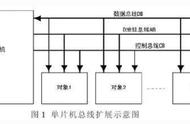

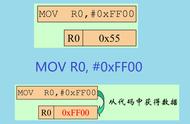

MCS-51单片机的P0端口可以作为地址总线低8位和数据总线,P2端口可作为地址总线高8位,其逻辑结构如图2-3所示。电路中包含一个数据输出锁存器和两个三态数据输入缓冲器,还有一个数据输出的驱动和控制电路。这两组线用作CPU与外部存储器(程序/数据)和I/O端口扩展时的数据总线和地址总线,其中P0、P2端口可以构成16位地址总线。此外,在读取外部存储器数据时,P0端口既作为低8位地址总线,也作为8位数据总线使用,即地址总线与数据总线采用分时复用,这一特点与8086微处理器的AD0~AD15相同。CPU输出地址时,由地址锁存信号ALE通知地址锁存芯片(如74LS573/74LS373)锁存P0.0~P0.7引脚上的地址信息。

图2-3 P0与P2端口的逻辑结构

P2端口作为外部数据存储器或程序存储器的地址总线的高8位输出(A8~A15),选通高位地址。P0端口作为低8位地址总线的输出,选通低位地址。当读取外部存储器数据时,P0端口送出低8位地址,同时P2端口送出高8位地址,合成16位地址信息。此时,ALE控制时序,先将低8位地址锁存,等外部存储器获取到地址信息后,P0端口随即送出或者读取8位数据。外部的程序存储器由PSEN信号选通,数据存储器则由

图2-4所示为P1和P3端口逻辑结构。P1端口为8位准双向端口,每一位均可单独定义为输入或输出端口。当作为输入端口时,1写入锁存器,Q(非)=0,T2截止,内上拉电阻将电位拉至“1”,此时该端口输出1;当0写入锁存器,Q(非)=1,T2导通,输出0。

作为输入端口时,锁存器置1,Q(非)=0,T2截止,此时该位既可以把外部电路拉成低电平,也可由内部上拉电阻拉成高电平,因此P1端口称为准双向端口。作为输入端口使用时,有两种情况,一种是读锁存器的内容,进行处理后再写到锁存器中,这种操作是读→修改→写操作,如JBC(逻辑判断)、CPL(取反)、INC(递增)、DEC(递减)、ANL(与逻辑)和ORL(逻辑或)指令均属于这类操作。另一种是读P1端口状态时,打开三态门G2,将外部状态读入CPU。

P3端口为准双向端口。P3端口的输入/输出、锁存器、中断、定时器/计数器、串行口与特殊功能寄存器有关。P3端口的第一功能和P1端口一样,可作为输入/输出端口,同样具有字节操作和位操作两种方式,在位操作模式下,每一位均可定义为输入或输出。P3端口第二功能表见表2-2。在MCS-51单片机实际应用场合中,P3端口的第二功能显得更为重要。