(1)电路组成及工作原理:

N沟道MOS管T作为采样开关用。当控制信号比为高电平时,T导通,输入信号VL经电阻Ri和T向电容Ch充电。若取Ri=Rf则充电结束后Vo=-Vi=VC。当控制信号返回低电平,T截止。由于Ch无放电回路,所以Vo的数值被保存下来。缺点:采样过程中需要通过Ri和T向Ch充电,所以使采样速度受到了限制。同时,Ri的数值又不允许取得很小,否则会进一步降低采样电路的输入电阻。

(2) 改进电路及其工作原理

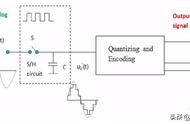

上图是单片集成采样-保持电路LE198的电路原理图及符号,它是一个经过改进的采样保持电路。图中A1,A2是两个运算放大器, S是电子开关, L是开关的驱动电路,当逻辑输入VL为1,即以为高电平时, S闭合;VL为0,即低电平时,S断开。

当 S闭合时, A1,A2 均作在单位增益的电压跟随器状态, 所以Vo=V'o=VI 如果将电容 Ch接到R2的引出端和地之间,则电容上的电压也等于VI。当VL返回低电平以后,虽然S断开了,但由于Ch上的电压不变,所以输出电压Vo的数值得以保持下来。

在S再次闭合以前的这段时间里,如果VL发生变化,V'o可能变化非常大,甚至会超过开关电路所能承受的电压,因此需要增加D1,和D2构成保护电路。当V'o比Vo所保持的电压高 (或低)一个二极管的压降时, D1(或D2)导通,从而将V'o限制在VI VD以内。而在开关s闭合的情况下,V'o和Vo相等,故D1和D2均不导通,保护电路不起作用。

二、AD比较器的类型直接AD转换器直接A/D转换器能把输入的模拟电压直接转换成输出的数字量而不需要经过中间变量。常用的电路有并行比较型和反馈比较型两类。

(1) 并行比较型AD转换器

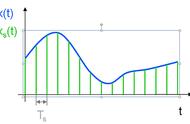

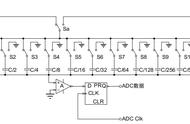

三位并行比较型A/D转换原理电路如下图所示,它由电压比较器、寄存器和代码转换器三部分组成。电压比较器中量化电平的划分采用上一期中量化和编码中的图(b)所示的方式,用电阻链把参考电压D2VREF压,得到从1/15VREF~13/15VREF之间7个比较电平,量化单位为2/15VREF.然后,把这7个比较电平分别接到7个比较器C1~C7,的输入端作为比较基准。同时将要输入的模拟电压同时加到每个比较器的另一个输入端上,与这7个比较基准进行比较。

单片集成并行比较型A/D转换器的产品较多,如AD公司的AD9012 (8位)、AD9002 (8位) AD9020 (10 位)等.

并行AD转换器具有如下特点:

①由于转换是并行的,其转换时间只受比较器、触发器和编码电路延迟时间限制,因此· 转换速度快。

②随着分辨率的提高,元件数目要按几何级数增加。一个n位转换器,所用的比较器个数为2的n次方-1,如8位的并行AD转换器就需要2的8次方-1等于255个比较器。由于位数愈多,电路愈复杂,因此制成分辨率较高的集成并行A/D转换器是比较困难的。

③使用这种含有寄存器的并行AD转换电路时,可以不用附加采样-保持电路,因为比较器和寄存器这两部分也兼有采样-保持功能,这也是该电路的一个优点。

下面是三位并行A/D转换器输入与输出转换关系对换表

并行比较型A/D转换器的缺点:需要用很多的电压比较器和触发器。从并行比较型AD转换图得知,输出为n位二进制代码的转换器中应当有2的n次方-1个电压比较器和2的n次方-1个触发器。电路的规模随着输出代码位数的增加而急剧增加。如果输出为10位二进制代码,则需要用2的10次方-1等于1023个比较器和1023个触发器以及一个规模相当大的代码转换电路。

好了今天的内容就到这了,下期给大家分享反馈比较型AD转换器和间接AD转换器,喜欢的朋友欢迎关注转发点赞哦

,