在Xe-LP上,Intel大刀阔斧的对EU内部进行了调整,首先Gen 11的一对一的线程控制单元现在变成一对二了,也就是一个线程控制单元实际要负责两个EU的任务。再往下,到具体的ALU上面,现在每个EU中含有8个用于处理浮点或整数指令的ALU,另外还有两个只针对扩展数学指令的ALU,从原本的4 4结构变成了8 2,而且两种类型的指令可以并行处理了。

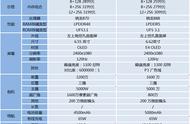

显示引擎方面,有四条4K分辨率级别的处理管线,支持两条eDP,外部输出接口则是支持DisplayPort 1.4和HDMI 2.0,当然,具体的输出接口可以是DP和HDMI,也可以是USB-C。其他像是8K输出、HDR10、Dolby Vision、12-bit BT2020色域和自适应同步都有支持,对显示器的刷新率,最高可以支持到360Hz。这里很可惜的是,我们没能见到原生的HDMI 2.1支持,厂商可能会通过转接芯片去做支持。

媒体引擎方面,整个处理管线的编解码性能提升了一倍,色深的支持升级到了12-bit,并且能够支持HDR/Dolby Vision的回放。这里还有一个亮点是对AV1做了硬件解码支持,这是一个面向于未来的特性。

目前大家见到的Xe核显以及那个DG1独显只是Intel的Xe计划的第一部,如无意外的话今明两年内我们会见到面向游戏玩家的Xe-HPG进入市场,届时我们将会在独显市场见到三足鼎立的情景。

其实Intel在早期CPU与核显的搭配是有些问题的,越强的CPU配越强的核显,但实际需求明显是反过来的,还好这个问题早就改过来了,现在的11代酷睿处理器就很明显,只有四核的Tiger Lake-U配的是拥有96组EU的GT2核显,而Rocket Lake-S与Tiger Lake-H这些八核处理器则只配32组EU的GT1核显,因为Tiger Lake-U是用在轻薄本的,多数没有独显,得靠自己的核显,而Rocket Lake-S与Tiger Lake-H则多数会配独显,核显的性能就显得不那么重要了,稍微精简一点也没所谓。

下一代的Alder Lake会继续使用Xe架构,同样的核心数量更少的Alder Lake-P会配更强劲的GT2级别核显,核心数量更多的Alder Lake-S则配GT1级别核显,再下一代的Raptor Lake估计会用改良的版本。至于Xe架构以后会如何进化,由于Intel从AMD的图形部门挖了不少人,所以大家其实可以参考AMD的GCN,预计会一步步慢慢优化挖掘Xe架构的潜能,当然以Intel的家底,一边优化Xe的同时并行开发另一种架构的GPU不是不可能的。