当晶振在并联谐振状态下工作时,线路表现为纯感性。在这种模式下,工作频率由晶振的负载决定。对于并联谐振状态的晶振,晶振制造商应该指定负载电容CL。在这种模式下,谐振频率:

在并联谐振模式下,电抗线中fs到fa的斜线区域内,通过调整晶振的负载,晶振都可以振荡起来。

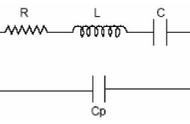

晶振电路

晶振振荡电路图如下图所示。这样的组成可以使晶振处于并联谐振模式。反相器提供了180°的相移,晶振、R1、C1、C2组成的π型网络产生另外180°的相移。所以整个环路的相移为360°。这满足了保持振荡的一个条件。另外一个条件是要求闭环增益应≥1,才能正确起振和保持振荡。

电阻Rf产生负反馈,它将反相器设定在中间补偿区附近,使反相器工作在高增益线性区域。电阻值很高,范围通常在500KΩ ~2MΩ内。图示的C1,C2就是为晶振工作在并联谐振状态下得到负载电容CL的电容。关于最优的负载电容CL的计算公式为:

其中Cs为PCB中晶振引脚寄生电容,典型值为2-5pF。通常C1,C2值取值相等。R1是驱动限流电阻,主要功能是限制反相器输出,这样晶振不会被过驱动(over driven)。R1、C1组构成分压电路,这些元器件的数值是以这样的方式进行计算的:反相器的输出接近rail-to-rail值,输入到晶振的信号是rail-to-rail的60%,通常实际是令R1的电阻值和的C1容抗值相等,即R1 ≈ XC1。这使晶振只取得反相器输出信号的一半。要一直保证晶振消耗的功率在厂商说明书规定范围内,过驱动会损坏晶振。

一般情况下,增大负载电容会使振荡频率下降,而减小负载电容会使振荡频率升高。 参考下图: