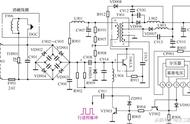

电路输入脉冲信号uin通过分压电路之后进入高速可调比较微分电路。高速可调比较微分电路输入端信号如图5所示,其中u 为运算放大器同相端输入信号,u-为运算放大器反相端输入信号。同相端信号u 由电容C1和电阻R3控制。反相端信号u-为电压比较点,由电阻R2和电位器RW2控制,通过调节RW2实时改变电压比较点,进而改变运算放大器输出脉冲的脉宽。高速可调比较微分电路输出信号如图6中u1所示,与输入脉冲信号uin对比脉冲信号u1正占空比明显减少。

脉冲正向整流及上下沿时间控制输出信号如图6中uo1所示,由于仿真电路中器件为理想器件,因此D1、D2、D3开关速度对脉冲信号上下沿延时的控制作用无法从仿真波形中呈现,仿真主要体现了对输入脉冲信号的整流作用。

脉冲信号传输延时调整及抗干扰电路仿真波形图如图6中uo2所示,通过与uo1对比可明显看出uo2相位后移,两者延时约100 ns,波形干净利落,抗干扰能力提高,实现信号的传输延时调整及抑制干扰。

2.2 电路实物与测试结果

高性能脉冲处理电路模块如图7所示,设计制作的PCB按频率0.6 GHz的高频线性电路设计方法进行高性能脉冲处理电路印制电路板的布局和走线[16];印制电路板按高速信号完整性和电源完整性的布局和布线方法进行布局和走线,有效进行模拟地和数字地的分割与桥接,4层印刷电路板有效减少印制电路板上的分布电感和分布电容,减小其形成的传输延时、脉冲上下沿时间,同时解决高幅值衰减振荡和高频辐射干扰问题,模块中元器件排列紧凑,模块尺寸仅50 mm×50 mm。

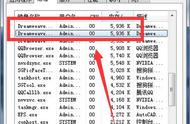

对设计制作的电路进行性能测试,使用的仪器包括:YB1731A直流稳压电源,DF1641A函数发生器,UTD7102B示波器,MT-1280数字万用表。

使用函数发生器产生脉冲信号uin,频率1 MHz,峰峰值24 V,上下沿延时约80 ns,正占空比约50%。输入脉冲信号首先通过电平转换及脉宽调整电路,再通过脉冲正向整流电路,其测试结果如图8所示。图8中示波器CH1通道为电平转换后的脉冲信号,频率1 MHz,峰峰值10 V,上下沿延时间约80 ns,正占空比50.5%。图8中示波器CH2通道为脉宽调整及整流后的脉冲信号,通过调节电位器RW2改变比较微分电路的比较点实现了脉冲信号脉宽实时可调,图8中(a)、(b)、(c)CH2通道测量显示占空比为28.6%、50%、53.1%;运算放大器电源电压为正负5 V,通过正向整流后将脉冲信号电压控制在0至5 V之间,频率保持1 MHz不变。在实际运用中可根据需要改变电容C1,电阻R2、R3以及电位器Rw2从而控制脉冲信号脉宽的可调范围,选取合适的运算放大器及其电源电压控制输出脉冲电压最大值。

通过上下沿延时控制电路,实现上下沿延时的控制,测试结果如图9所示。输入脉冲信号CH1上下沿延时间84 ns,输出脉冲信号CH2上升时间23 ns、下降时间56 ns,频率1 MHz。由测量波形可直观看出脉冲信号上下沿陡度明显提高,上下沿时间缩短。与仿真相比,客观地反应了D1、D2、D3开关速度对电路上下沿时间的影响。