在电子技术中,N/2(N为奇数)分频电路有着重要的应用,对一个特定的输入频率,要经N/2分频后才能得到所需要的输出,这就要求电路具有N/2的非整数倍的分频功能。

一、CD4013功能概述

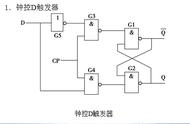

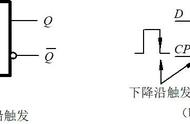

双D触发器CD4013是一双D触发器,由两个相同的、相互独立的数据型触发器构成。每个触发器有独立的数据、置位、复位、时钟输入和Q及Q\输出,此器件可用作移位寄存器,且通过将Q输出连接到数据输入,可用作计算器和触发器。在时钟上升沿触发时,加在D输入端的逻辑电平传送到Q输出端。置位和复位与时钟无关,而分别由置位或复位线上的高电平完成。

二、CD4013引脚排列图

CD4013内部含有二个D触发器,我们分别称为1号和2号。

1脚:1号D触发器的输出端1Q。

2脚:1号D触发器的输出端1Q\,与1脚输出状态相反。

3脚:1号D触发器的时钟信号输入端1CP,上升沿有效。

4脚:1号D触发器的置0输入端1RD,高电平有效。

5脚:1号D触发器的数据输入端1D。

6脚:1号D触发器的置1输入端1SD,高电平有效。

7脚:CD4013的电源端,接电源负极或地。

8脚:2号D触发器的置1输入端2SD,高电平有效。

9脚:2号D触发器的数据输入端2D。

10脚:2号D触发器的置0输入端2RD,高电平有效。

11脚:2号D触发器的时钟信号输入端2CP,上升沿有效。

12脚:2号D触发器的输出端2Q\,与13脚输出状态相反。

13脚:2号D触发器的输出端2Q。

14脚:CD4013的电源接端,接电源正极。

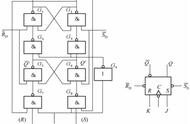

从以上几个N/2分频电路可得到如下几个特性:

1.电路工作原理是,在第n个周期,末级两分频器的输出为高电平时,输入时钟脉冲的上升沿使分频电路工作;在第n 1个周期,末级两分频器的输出为低电平时,输入时钟脉冲的下降沿使分频电路工作。

2.电路采用的是异步触发形式,各触发器的初始状态不会影响到分频的功能。如果要求初始状态为"0"状态,可以将D触发器的复位端R引出,接至复位控制电路。

3.输入信号fi的最高工作频率fimax除受到CMOS元件fM的限制外,还受到D触发器、反馈门翻转延迟和电容C滤波频率特性的影响,所以应尽可能提高fi的值。一般情况下,最高工作频率fimax在几百千赫以下。用CD4013双D触发器做的脉冲4分频器

CD4013组成的4分频电路

,