一、JK触发器

1.1 电路组成和逻辑符号

克服在R=S=1时出现不定状态的另一种方法:将触发器输出端Q和 状态反馈到输入端,这样,G3和G4的输出不会同时出现0,从而避免了不定状态的出现。

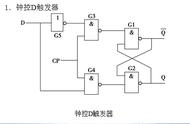

JK触发器的逻辑电路如图1(a)所示。图1(b)是它的逻辑符号图。

图1 JK触发器

小常识:图1(b)逻辑符号加小圆圈表示下降沿有效触发;不加小圆圈表示上升沿有效触发。

1.2 逻辑功能

(1)J=0,K=0,Qn 1=Qn

这时,门G7,G8均被封锁。CP脉冲到来后,触发器的状态并不翻转,即Qn 1=Qn,输出保持原态不变。

(2)J=1,K=1,Qn 1=/Qn

这时,输入均为高电平或J,K端都悬空,不加输入信号。因为S=/Qn ,R=Qn,电路和计数型RS触发器相似。每当CP脉冲下降沿到来后,触发器的状态就发生翻转,Qn 1=/Qn 。随着CP脉冲不断输入,触发器的状态不断翻转,实现了计数功能。

(3)J=1,K=0,Qn 1=1

如果触发器原态为Qn=0,/Qn =1。那么在CP=1时,门G7输出1,G8输出0。所以主触发器为1态,即Qn 1=1,/Qn 1=0。

当CP脉冲下降沿到来后,主触发器的状态就转存到从触发器中,电路状态翻转为1态,即Qn 1=1。

(4)J=0,K=1,Qn 1=0

仿照上述的方法分析,可以得知,不论触发器原来状态如何,当CP脉冲到来后,触发器置0,即Qn 1=0。

根据以上的分析,JK触发器的逻辑功能见表1,功能时序图如图2。

表1 JK触发器真值表

图2 JK触发器时序图

二、D触发器和T触发器

2.1 D触发器

2.1.1 电路组成

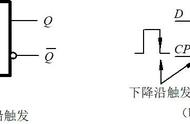

将JK触发器J端信号,通过非门G接到K端,即使K= /J。触发器的输入信号从J端加入,这就构成了D触发器。电路如图3(a)所示,图3(b)所示为它的逻辑符号。