鉴于上面可编程 I/O 的缺陷,我们提出一种改良方案,我们想要在 CPU 等待 I/O 设备的同时,能够做其他事情,等到 I/O 设备完成后,它就会产生一个中断,这个中断会停止当前进程并保存当前的状态。一个可能的示意图如下

尽管中断减轻了 CPU 和 I/O 设备的等待时间的负担,但是由于还需要在 CPU 和 I/O 模块之前进行大量的逐字传输,因此在大量数据传输中效率仍然很低。下面是中断的基本操作

- CPU 进行读取操作

- I/O 设备从外围设备获取数据,同时 CPU 执行其他操作

- I/O 设备中断通知 CPU

- CPU 请求数据

- I/O 模块传输数据

所以我们现在着手需要解决的就是 CPU 和 I/O 模块间数据传输的效率问题。

使用 DMA 的 I/ODMA 的中文名称是直接内存访问,它意味着 CPU 授予 I/O 模块权限在不涉及 CPU 的情况下读取或写入内存。也就是 DMA 可以不需要 CPU 的参与。这个过程由称为 DMA 控制器(DMAC)的芯片管理。由于 DMA 设备可以直接在内存之间传输数据,而不是使用 CPU 作为中介,因此可以缓解总线上的拥塞。DMA 通过允许 CPU 执行任务,同时 DMA 系统通过系统和内存总线传输数据来提高系统并发性。

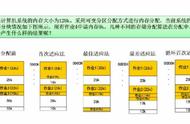

I/O 层次结构I/O 软件通常组织成四个层次,它们的大致结构如下图所示

每一层和其上下层都有明确的功能和接口。下面我们采用和计算机网络相反的套路,即自下而上的了解一下这些程序。

下面是另一幅图,这幅图显示了输入/输出软件系统所有层及其主要功能。

下面我们具体的来探讨一下上面的层次结构

中断处理程序在计算机系统中,中断就像女人的脾气一样无时无刻都在产生,中断的出现往往是让人很不爽的。中断处理程序又被称为中断服务程序 或者是 ISR(Interrupt Service Routines),它是最靠近硬件的一层。中断处理程序由硬件中断、软件中断或者是软件异常启动产生的中断,用于实现设备驱动程序或受保护的操作模式(例如系统调用)之间的转换。

中断处理程序负责处理中断发生时的所有操作,操作完成后阻塞,然后启动中断驱动程序来解决阻塞。通常会有三种通知方式,依赖于不同的具体实现

- 信号量实现中:在信号量上使用 up 进行通知;

- 管程实现:对管程中的条件变量执行 signal 操作

- 还有一些情况是发送一些消息

不管哪种方式都是为了让阻塞的中断处理程序恢复运行。

中断处理方案有很多种,下面是 《ARM System Developer’s Guide

Designing and Optimizing System Software》列出来的一些方案

- 非嵌套的中断处理程序按照顺序处理各个中断,非嵌套的中断处理程序也是最简单的中断处理

- 嵌套的中断处理程序会处理多个中断而无需分配优先级

- 可重入的中断处理程序可使用优先级处理多个中断

- 简单优先级中断处理程序可处理简单的中断

- 标准优先级中断处理程序比低优先级的中断处理程序在更短的时间能够处理优先级更高的中断

- 高优先级 中断处理程序在短时间能够处理优先级更高的任务,并直接进入特定的服务例程。

- 优先级分组中断处理程序能够处理不同优先级的中断任务

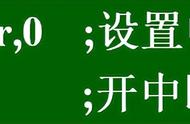

下面是一些通用的中断处理程序的步骤,不同的操作系统实现细节不一样

- 保存所有没有被中断硬件保存的寄存器

- 为中断服务程序设置上下文环境,可能包括设置 TLB、MMU 和页表,如果不太了解这三个概念,请参考另外一篇文章

- 为中断服务程序设置栈

- 对中断控制器作出响应,如果不存在集中的中断控制器,则继续响应中断

- 把寄存器从保存它的地方拷贝到进程表中

- 运行中断服务程序,它会从发出中断的设备控制器的寄存器中提取信息

- 操作系统会选择一个合适的进程来运行。如果中断造成了一些优先级更高的进程变为就绪态,则选择运行这些优先级高的进程

- 为进程设置 MMU 上下文,可能也会需要 TLB,根据实际情况决定

- 加载进程的寄存器,包括 PSW 寄存器

- 开始运行新的进程

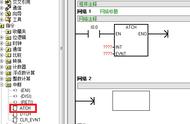

上面我们罗列了一些大致的中断步骤,不同性质的操作系统和中断处理程序能够处理的中断步骤和细节也不尽相同,下面是一个嵌套中断的具体运行步骤