在这种实现下,虚拟机里只跑驱动的用户空间,所有涉及核心空间的调用全都扔到Hypervisor。这要求hypervisor本身是Linux,只有KVM符合这个要求。Arm的Mali图形处理器,硬件上是支持指定某个渲染核心跑特定任务的,也就是可以把某个虚拟机的任务运行在特定渲染核心的。这样,如果有实时性的操纵系统要跑,比如仪表盘,可以保留出一个核来,不被其他虚拟机抢占,来实现一定程度的QoS。此时,图形处理器是真正同时跑两个虚拟机任务的,而不是时分复用。至于输出的frame buffer,不同的任务是可以放到不同物理地址的,只是没法区分SteamID,没法做隔离。

Arm支持硬件虚拟化的图形处理器估计还要一年才会出来。具体到细节,虚拟化除了需要寄存器分组,缓存对vmid敏感之外,通用的一些单元也需要支持分组。

关于虚拟机的效率,还有两点需要注意:Arm现有的中断控制器GIC600,受限于GICv3.x协议,是没有办法绕过hypervisor,直接把虚拟中断送到Guest OS的。外部中断送进来,还是得经由hypervisor权限设置寄存器,产生一个虚拟中断到Guest OS。中断直接送到Guest OS要到GICv4才会改进。

Armv8.1及之后的CPU,都支持一个叫VHE的机制,可以加速2型虚拟机的切换。具体原理是,KVM等2型虚拟机,Hypervisor就在Linux核心里面,而Linux需要完整的2阶3/4层页表。另外一方面,Armv8.1之前的处理器EL2没有对应的页表。如果没有VHE,那这个Hypervisor必须把一部分驻留在EL2做高权限操作,而Host Linux还是运行在EL1。这样,很多操作需要从EL1陷入EL2,改完再回到EL1的Linux核心,多了一层跳转。有了VHE,那么Host Linux核心直接运行在EL2,可以操作EL1的4层页表的页表寄存器,软件上不用做修改。硬件上,这些访问会被重定向到EL2,以保证权限。

对于1型虚拟机,比如Xen,这个改动没有影响。这里我们要提一下QNX的虚拟机,它是1型虚拟机。QNX是目前唯一一个能达到Asil-D等级的操作系统(包含Hypervisor)。如果需要实现Asil-D级别的系统,必须把现有的软件从Linux系统移植到QNX。所幸的是,QNX也是符合Posix标准的,尤其是图形处理器的驱动,移植起来会省事一些。QNX不是所有的模块都是Asil-D级,移植过去的驱动,其实是没有安全等级的。QNX依靠Asil-D级的核心软件模块和Hypervisor,保证99%以上的失效覆盖率。如果子模块出了问题,那只能重启子模块。

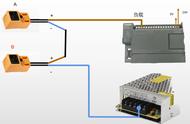

前面说到,有些厂商认为虚拟化还不够,有些场景要物理隔离。虚拟化的时候,硬件资源还是共享的,只不过对软件是透明。这样其实并不能完全防止硬件的冲突和保证优先级。请注意,硬件隔离是separation,而不是分区partition,Partition是用MPU来做的。在中控的系统框架图内,我们把采用物理隔离的红色部分单独列出来,如下图:

此时的处理器A55和图形处理器G31,独立于作为信息娱乐域的处理器A76/A55和图形处理器G76之外,拥有自己的电源,时钟和电压。作为优化,红色部分可以和其余的处理器用一致性总线连接起来,在不作为仪表盘应用的时候,作为SMP的一部分来使用。而需要隔离的时候,用多路选择连接到NoC或者内存控制器。这样既节省了面积,又实现了隔离。

同样的,图形处理器也有物理隔离的需求。实现其实并不复杂,比支持硬件虚拟化要直接,如下图:

由于图形处理器面积最大的是渲染核心SC,这部分不动。其余的硬件模块,每组核都复制一份,组和组之间用内部总线ASN互联。当拆成多个图形处理器的时候,每个冗余模块分别控制自己的资源。此时,每组GPU需要独立运行一个驱动。而把所有资源融合运行的时候,冗余的部分自动关闭,由一个模块集中调度。此时,某些公用资源可能会遇到性能瓶颈,但汽车通常只会要求物理隔离两个组,分别给仪表盘和信息娱乐,并且仪表盘所需资源较少,融合的时候,可以启用信息娱乐的共享单元,从而避免瓶颈。对于系统中其余的主设备,也可以利用类似的设计思路来实现隔离。

有了同时支持虚拟化和硬件隔离的图形处理器,我们的中控芯片构架会有如下改动:

此时图形处理器的物理隔离和硬件虚拟化可以同时启用,跑多份驱动,满足前文的需求。

至此,虚拟化和隔离结束,开始讨论车规。

目前我们说的车规分两个,功能安全和电气标准。前者由ISO26262定义,后者由AEC-Q100定义。

功能安全在芯片上的设计原则是要尽可能多的找出芯片上的失效场景并纠正。失效又分为系统和随机两种,前者依靠设计时的流程规范来保证,后者依赖于芯片设计上采取的种种失效探测机制来保证。我们在这主要谈后者。

简单来说,芯片的失效率,是基于单个晶体管在某个工艺节点的失效概率,推导出片上逻辑或者内存的失效概率。面积越大,晶体管越多,相应的失效率越大。ISO26262把安全等级做了划分,常见的有ASIL-B和ASIL-D级。ASIL-B要求芯片能够覆盖90%的单点失效场景,而ASIL-D则是99%。这其实是个非常高的要求。一个晶体管的失效概率虽低,可是通常一个复杂芯片是上亿个晶体管组成的,如果不采取任何措施,那任何一点的错误都可能造成功能失效,失效率很高。

ISO26262手册第五篇的附件D,详细描述了硬件失效的探测手段。在这部分,硬件系统被分为几个模块:输入端有传感器,连接件,中继,数模接口;处理部分包含处理单元,各类内存闪存。系统层面有总线,电源和时钟。系统框架如下图: