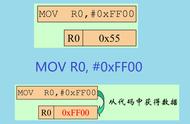

如果将DPTR寄存器拆分为两个独立的8位寄存器DPH和DPL,则MCS-51单片机主要有27个特殊功能寄存器,其中8051系列有11个寄存器具有位寻址功能,8052系列单片机由于扩展了一个定时器/计数器,则有12个寄存器具有位寻址功能,这些寄存器中的每一位都具有位地址,具有定义的位可以直接按位访问,可进行位寻址的SFR的分布见表2-8所列。需要注意的是,PC不占据RAM单元,在物理上是独立的,因此是不可寻址的寄存器。对专用寄存器只能使用直接寻址方式,编写程序的时候既可使用寄存器符号,也可使用寄存器单元地址。内部RAM及特殊功能寄存器各存储单元之间的数据传送用MOV指令。

表2-8 8051和8052系列单片机中可进行位寻址的SFR的分布

续表

注:表2-8中“—”表示该位没有使用,不能用指令进行读写操作;“*”表示该二进制位没有特殊含义,仅仅代表该寄存器的某一个二进制位,可以通过指令读写该位数据。

表2-5中,R0~R7寄存器组在汇编程序中可以通过设置RS1、RS0两个位,将寄存器分配到不同工作寄存器区,不同工作寄存器区的通用寄存器Rn(n=0~7)尽管编号n相同,但具有不同的RAM地址,因此通用寄存器共有8×4=32个。

表2-7中,寄存器T2CON、T2MOD、RCAP2L、RCAP2H、TL2、TH2是8052系列单片机扩展的定时器/计数器2的寄存器,在8051系列单片机中不存在。

由表2-8可知,能够按位访问的SFR其字节地址均为8的倍数,且每个SFR的字节地址为该寄存器最低位的位地址。比如:P2寄存器的字节地址为0A0H,最低位P2.0的位地址也是0A0H。由表2-6和表2-8可知,MCS-51单片机可以按位访问的位地址范围为00H~0F7H,其中位地址0AEH、0BEH、0BFH和0D1H共计4个位单元没有定义,读写操作没有意义;而ET2(0ADH)、PT2(0BDH)和T2CON的8个位适合具备定时器/计数器2的8052系列单片机,8051没有定时器/计数器2,读写操作没有意义。

3.外部数据存储器

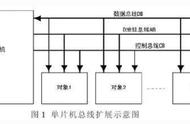

由于MCS-51单片机内部数据存储器只有128B,往往不够用,这就需要扩展外部数据存储器。外部数据存储器最多可以扩到64KB,16位数据指针寄存器作为间接寻址的寄存器的地址指针,其寻址范围为64KB。当外部数据存储器小于256B时,可用R1、R0作为间接寻址寄存器的地址指针。访问外部数据存储器或扩展I/O口可用MOVX指令。

2.2 MCS-51单片机时钟电路与总线时序

无论是通用微型计算机还是单片机,CPU所有的工作都是在时钟信号控制下进行的,每执行一条指令,CPU的控制器就要发出一系列特定的控制信号,这些控制信号在时间上的先后次序就是CPU的工作时序。

2.2.1 时钟电路

MCS-51单片机的时钟连接有两种方式,一种是内部时钟方式,但须在XTAL1和XTAL2引脚外接石英晶体(2~24MHz)和振荡电容,电容C1和C2对频率有微调作用,电容量的选择范围为5~30pF,如图2-7(a)所示。另一种是采用外部时钟方式,即将XTAL2引脚悬空,外部时钟信号(外部振荡器提供的信号)从XTAL1引脚输入,如图2-7(b)所示。

图2-7 MCS-51单片机的时钟连接方式

在单片机应用电路设计中,时钟电路器件应该尽可能靠近CPU对应引脚。如果CPU无法正常工作,可通过示波器检测CPU时钟引脚是否有一定幅值的时钟信号,如果有,则时钟电路正常。

2.2.2 总线时序

MCS-51单片机的振荡频率经过内部二分频以后得到的信号周期,称为状态周期,即一个状态周期包括两拍的时钟周期。机器周期就是计算机完成一种基本操作所需的时间。MCS-51单片机的机器周期由6个状态周期组成,即S1~S6,而每个状态又分为两拍,称为P1和P2,因此一个机器周期中的12个振荡周期常可表示为S1P1、S1P2、…、S6P1、S6P2。若采用12MHz的晶体振荡器,则每个机器周期为12×106/(12×106)=1μs,若采用6MHz晶体振荡器,则每个机器周期为2μs。

在MCS-51单片机指令系统中,有单字节指令、双字节指令和三字节指令。每条指令的执行时间分别占用1个或几个机器周期。单字节指令和双字节指令都可能是单机器周期和双机器周期的,而三字节指令都是双机器周期的,只有乘、除法指令占用4个机器周期。

每一条指令的执行都包括取指令和执行指令两个阶段。在取指令阶段,CPU从程序存储器中取出指令操作码及操作数,然后执行这条指令的逻辑功能。对于绝大部分指令,在整个指令执行过程中,ALE是周期性的信号,如图2-8所示。在每个机器周期中,ALE信号出现两次:第一次在S1P2和S2P1期间,第二次在S4P2和S5P1期间。ALE信号的有效宽度为1个S状态。每出现一次ALE信号,CPU就进行一次取指令操作。