各位朋友,今天我们来讲解持续模型和持续路径。图中标注的一二、三四四种路径都属于失去路径。其中,贴片路径包括路径一、三,贴片内路径则是路径二、四。

路径一的约束是set、input、delete,用于表示从输入端口到FPGA内部第一级触发器的路径。

路径二的约束是create clock,用于表示从f、PC内部触发器之间的路径。

路径三的约束是fat output delay,用于表示从f、peng内部笔迹处罚器到输出端口的路径。

路径四的约束是such max之类,用于表示从f、pin g输入端口到输出端口的路径。

在这四类路径中,我们最需要关注的是路径二的同步失去路径,也就是fpj内部的失去逻辑。接下来,我们来看看失去模型。

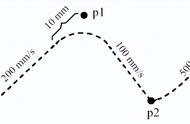

一个完整的数据模型包括原始中路径、数据路径和目的始终路径,可以用处罚器加组合逻辑加处罚器的模型来表示。持续模型的要求是t c o加t logic加t lo加routine加t fight up减去一个t skill,必须小于等于t clk。其中,t c o是发端计算器的时钟到输出时间,t logic是组合逻辑延时,t rooting是两个计算器之间的布线延时,t set up是收端处罚器的建立时间。t skill是两级计算器的时钟歪斜,等于时钟边沿同时到达两个计算器端口的时间差,tclk是系统所能达到的最小时钟周期。