3.HDL代码设计及仿真验证

设计代码:

`timescale 1ns / 1ps

module cordic_ex#(parameter DIN_W = 16,

DOUT_W = 16)

(

input clk,

input [DIN_W-1:0] din,//2Q13

input din_vld,

output reg [DOUT_W 1-1:0] dout = 0,//2Q14

output reg dout_vld = 0

);

wire [DOUT_W*2-1 : 0] m_axis_dout_tdata;

wire m_axis_dout_tvalid;

wire signed [DOUT_W-1:0] sinh,cosh;

// ex = sinhx coshx <1Q14 1Q14 = 2Q14>

always @(posedge clk)begin

dout <= sinh cosh;

end

assign sinh = m_axis_dout_tdata[DOUT_W*2-1 -:DOUT_W];

assign cosh = m_axis_dout_tdata[DOUT_W-1 -:DOUT_W];

always @(posedge clk)begin

if(m_axis_dout_tvalid)begin

dout_vld <= 1'b1;

end

else

dout_vld <= 0;

end

cordic_0 cordic_cosh_sinh (

.aclk(clk), // input wire aclk

.s_axis_phase_tvalid(din_vld), // input wire s_axis_phase_tvalid

.s_axis_phase_tdata(din), // input wire [15 : 0] s_axis_phase_tdata

.m_axis_dout_tvalid(m_axis_dout_tvalid), // output wire m_axis_dout_tvalid

.m_axis_dout_tdata(m_axis_dout_tdata) // output wire [31 : 0] m_axis_dout_tdata

);

endmodule

cordic_ex

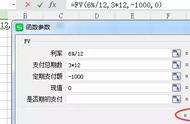

用MATLAB产生两组数据,并将角度值定点化后作为设计模块数据激励:

testbench:

`timescale 1ns / 1ps

module cordic_ex_tb();

parameter CYC = 20;

reg clk;

reg [16-1:0] din;

reg din_vld;

wire signed [17-1:0] dout;

wire dout_vld;

cordic_ex#(.DIN_W(16),

.DOUT_W(16))

uut(

.clk (clk) ,

.din (din) ,//2Q13

.din_vld (din_vld) ,

.dout (dout) ,//2Q14

.dout_vld (dout_vld)

);

initial begin

clk = 1;

forever #(CYC/2) clk = ~clk;

end

initial begin

#1;

din = 0;

din_vld = 0;

#(CYC*10);

din_vld = 1;

din = 16'b0001010000011011;//pi * 1/5

#(CYC*1);

din = 16'b1110011011011110;//-pi * 1/4

#5;

$stop;

end

endmodule

cordic_ex_tb

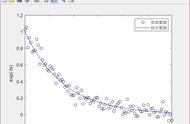

仿真结果:

仿真波形表明,计算结果与MATLAB浮点运算相近,满足一般计算需求。若想提高精度,可以增加CORDIC输出数据位宽。