早些年的时候,芯片技术节点确实是遵从着“摩尔定律”来进行命名的。即每当工艺节点的尺寸缩小至原先的0.7倍时,就是新技术节点的命名之时,比如90纳米、65纳米、45纳米、32纳米,都是在同样面积下,比上一级技术节点尺寸放下两倍多的晶体管。

摩尔定律

但接下来,在更小的尺寸命名时,大概是技术进步变得更艰难的缘故,有些公司就开始变得“没原则”了,在晶体管密度上仅仅向前蹭了微不足道的一小步时,也敢腆着大脸直接冠上一个更小的尺寸节点来吸引眼球。从此,技术节点的命名就与“摩尔定律”脱节了。

这个混淆命名视听的窍门,就是故意混淆芯片上晶体管的尺寸与工厂生产使用的技术尺寸。在早年的时候,晶体管尺寸和工厂生产尺寸没有差距,所以命名上就没有问题。但自32纳米以后,工厂的生产尺寸和晶体管尺寸就不一致了,此时开始,各个公司的命名就自说自话,与芯片的实际尺寸就没有关系了。

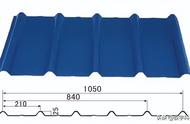

不同公司工艺尺寸下的晶体管密度

现在如果做芯片比较的话,实际上用晶体管密度来做比较可能更合理一点点。这就是为什么Intel的10纳米工艺与台积电/三星的7纳米工艺相比一点不差的原因,因为二者在同样面积上的晶体管密度相同。如果一定说有什么区别,那就是Intel的10纳米(Ice Lake)芯片现在产量还比较低,且仅能用在功耗敏感的笔记本电脑上,而台积电的7纳米工艺已经是铺天盖地地进行生产了,比如苹果A12、麒麟980、晓龙855和Ryzen3000系列等等。直接从爆产能上完败Intel。

Intel与台积电时间/技术节点对比

至此,如果Intel进化到7纳米节点,理论上的晶体管密度会超过台积电的5纳米而逊色与其3纳米,大约介乎于4纳米的位置上。这就是为什么业界,始终并不认为Intel已经被台积电和三星甩掉的原因,只是Intel没有台积电和三星那么“浮夸”吧了,虽然也在吹气球,但真没敢像台积电和三星那样使劲吹而已。

,