近日,据路透社报道,晶圆代工龙头台积电表示,预计将在5nm节点技术上投资250亿美元。而该制成节点也将会是台积电第 2 个采用 EUV 技术的制程节点。那么台积电5nm的应用主要对象是谁?要知道5nm的主要应用对象,就得先搞清5nm的定义究竟是什么?

实事求是的说,目前关于5nm的定义究竟是什么仍然成迷。因为,关于工艺节点的命名方法和定义仍然是模糊的。在对16nm/14nm的规格上代工厂商们的定义还是有出入的,所以我们才会看到,三星14nm LPP>台积电16nm FF >三星14nm FinFET>台积电20nm。同样的情形也可能发生在10nm和7nm上,但到5nm节点名称可能会变得无关紧要了。

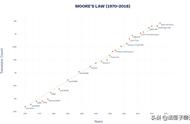

根据摩尔定律,每次节点的更替都是关键的晶体管规模尺寸缩小为原来的0.7倍或0.8倍,大约相当于晶体管密度翻倍。所以到了5nm时需要一个更有潜力的晶体管形式,芯片制造商们希望能够遵循由摩尔定律阐明的传统的晶体管缩放比例。在确定5nm节点规格上,使用的方法是参考英特尔14nm工艺规格并采取缩放0.7或0.8倍的方法。

据Intel的报告显示:Intel公司提出的下一代晶体管结构是纳米线FET,这是一种晶体管的一面让栅包围的finFET。Intel的纳米线FET有时被称为环栅FET,并己被国际工艺路线图ITRS定义为可实现5nm的工艺技术。

台积电的5nm它的应用主要对象是谁?Intel公司的报告似乎传递出一个信号,5nm可能有希望实现,或者已经在其工艺路线图中采用了新的晶体管结构。但在5纳米时,许多技术上的挑战,导致成本之高,让人们无法预计。此外,图形曝光技术是5nm节点面临的一个挑战;对5nm工艺而言,采用EUV(超紫外光刻技术)技术的成本更低。

在5纳米的竞争中,不甘落后的台积电表示,预计将在5nm节点技术上投资250亿美元;将在 2019 上半年展开风险试产,并且以手机与高性能运算芯片应用为主要对象。相较于第一版不采用EUV的7纳米制程,5nm节点的密度号称可达1.8倍,不过功耗预期只降低20%、速度约增加15%,采用极低阈值电压(Extremely Low Threshold Voltage, ELTV)技术则或许能提升25%;台积电并未提供ELTV技术的细节。

写在最后

从加利福尼亚技术学院Carver Mead教授将摩尔的预见性理论概括为摩尔定律至今已过去整整40年,近年来晶体管尺寸越来越小,芯片制作难度逐渐增加,摩尔定律何时失效使得人们忧虑。但物有本末,事有终始,半导体工艺终究会遇到难以跨越的障碍,到了那个时候,新的技术节点就再也不会出现了。尽管依靠庞大的人才和资金支持,不断有新材料、新工艺和新结构出现,使得半导体工艺度过了许多看似不可逾越的难关,但5nm必须具备一定的成本优势,否则,实现5纳米并没有多大意义。