芯片电学(零级封装)互连:

在一级封装中,有个很重要的步骤就是将芯片和封装体(进行电学互连的过程,通常称为芯片互连技术或者芯片组装。为了凸显其重要性,有些教科书也将其列为零级封装。也就是将芯片上的焊盘或凸点与封装体通常是引线框架用金属连接起来)。在微电子封装中,半导体器件的失效约有一是由于芯片互连引起的,其中包括芯片互连处的引线的短路和开路等,所以芯片互连对器件的可靠性非常重要。

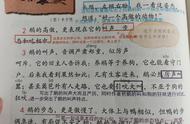

常见的芯片电学互连有三种方式,分别是引线键合,载带自动焊和倒装焊。

通常,TAB和FC虽然互连的电学性能要比好,但是都需要额外的设备。因此,对于I/O数目较少的芯片,TAB和FC成本很高,另外,在3D封装中,由于芯片堆叠,堆叠的芯片不能都倒扣在封装体上,只能通过WB与封装体之间进行互连。基于这些原因,到目前为止,WB一直是芯片互连的主流技术,在芯片电学互连中占据非常重要的地位。

芯片电学互连(零级封装)的三种方式

引线键合(WB)

引线键合(WB)是将芯片焊盘和对应的封装体上焊盘用细金属丝一一连接起来,每次连接一根,是最简单的一种芯片电学互连技术,按照电气连接方式来看属于有线键合。

载带自动焊(TAB)

载带自动焊(TAB)是一种将IC安装和互连到柔性金属化聚合物载带上的IC组装技术。载带内引线键合到IC上,外引线键合到常规封装或者PCB上,整个过程均自动完成,因此,效率比要高。按照电气连接方式来看属于无线键合方法。

倒装焊(FC)

倒装焊(FC)是指集成电路芯片的有源面朝下与载体或基板进行连接。芯片和基板之间的互连通过芯片上的凸点结构和基板上的键合材料来实现。这样可以同时实现机械互连和电学互连。同时为了提高互连的可靠性,在芯片和基板之间加上底部填料。对于高密度的芯片,倒装焊不论在成本还是性能上都有很强的优势,是芯片电学互连的发展趋势。按照电气连接方式来看属于无线键合方法。

半导体封装的典型封装工艺简介

依据封装管脚的排布方式、芯片与PCB板连接方式以及发展的时间先后顺序,半导体封装可划分为PTH封装(Pin-Through-Hole)和SMT封装(Surface-Mount-Technology)二大类,即通常所称的插孔式(或通孔式)和表面贴装式。

针脚插装技术(PTH):

针脚插装封装,顾名思义即在芯片与目标板的连接过程中使用插装方式,古老而经典DIP封装即属于该种封装形式。在早期集成电路中由于芯片集成度不高,芯片工作所需的输入/输出管脚数较少,所以多采用该种封装形式。DIP封装有两种衍生封装形式,即为:SIP和ZIP,只是为适应不同的应用领域,对传统DIP封装在封装壳管脚排布和形状上略有改进。

表面贴装封装(SMT):

PTH封装在机械连接强度上的优势毋庸质疑,但同时也带来一些负面效应。PTH封装中使用的贯通孔将大量占用PCB板有效布线面积,因此目前主流的PCB板设计中多使用表面贴片封装。

表面贴片封装有很多种类,常用的封装形式有:

小型塑封晶体管(Small Outline Transistor,SOT)

小引出线封装(Smal lOutline Package,SOP)

四方扁平无引线封装(Quad Flat No-lead Package,QFN)

薄小缩小外形封装(Thin Small Shrink Outline Package,TSSOP)

方型扁平式封装(Quad Flat Package,QFP)

方形扁平无引脚封装(QFN)

从SOT到QFN,芯片封装壳支持的管脚数越来越多,芯片封装壳的管角间距越来越小。

表面贴片封装方式的优点在于芯片封装的尺寸大大下降,芯片封装的管脚密度大大提升,与PTH封装具有相同管脚数量时,表面贴片封装的封装尺寸将远小于PTH封装。表面贴片封装只占用PCB板表层布线空间,在使用多层布线工艺时,封装占用的有效布线面积大大下降,可以大大提高PCB板布线密度和利用率。

BGA:

封装伴随着芯片集成度不断提高,为使芯片实现更复杂的功能,芯片所需的输入/输出管脚数量也进一步提升,面对日趋增长的管脚数量和日趋下降的芯片封装尺寸,微电子封装提出了一种新的封装形式BGA封装。