钱浩宇,汪鹏君,丁代鲁,张跃军

(宁波大学 电路与系统研究所,浙江 宁波315211)

通过对传统移位寄存器原理和灵敏放大型逻辑(Sense Amplifier Based Logic,SABL)电路的研究,提出一种能够防御差分功耗分析的移位寄存器设计方案。该方案首先采用主从触发的方式,设计基于SABL电路的清零置位D触发器;然后利用该触发器与SABL逻辑门实现多位移位寄存器电路。Spectre仿真验证表明,所设计的移位寄存器逻辑功能正确,在多种PVT组合下NED均低于2.66%、NSD均低于0.63%,具有显著的防御差分功耗分析性能。

SABL;防御差分功耗分析;移位寄存器;信息安全

中图分类号:TN918.4

文献标识码:A

DOI:10.16157/j.issn.0258-7998.2017.02.008

中文引用格式:钱浩宇,汪鹏君,丁代鲁,等. 基于SABL的防御差分功耗分析移位寄存器设计[J].电子技术应用,2017,43(2):40-43.

英文引用格式:Qian Haoyu,Wang Pengjun,Ding Dailu,et al. Design of resistant differential power analysis shift register based on SABL[J].Application of Electronic Technique,2017,43(2):40-43.

0 引言

随着信息安全技术的发展,以密码芯片为主要部件的便携式设备得到广泛应用。然而,在运行加密算法时密码芯片会泄露各种与所处理的数据本身相关的物理信息,如能量消耗、电磁辐射和运行时间等。这些物理信息可以被攻击者用来对密码芯片进行旁道攻击(Side Channel Attack,SCA)盗取密钥[1]。差分功耗分析(Differential Power Analysis,DPA)是旁道攻击中一种简单高效的攻击方法,极大降低了密码芯片的有效性[2]。近年来,学者们提出了多种防御DPA攻击技术,如双电压单轨动态逻辑(Dual-voltage Single-rail Dynamic Logic,DSDL)[3]、基于掩码的双轨预充逻辑(Masked Dual-Rail Pre-charge Logic,MDPL)[4]和灵敏放大型逻辑(Sense Amplifier Based Logic,SABL)[5]等。由于缺少对称的下拉网络,DSDL求值速度慢;文献[6]指出MDPL当输入信号之间存在延迟差异时,其防御DPA攻击性能较差。由于SABL具有工作速度快、防御DPA攻击性能好等特点,逐渐成为防御DPA攻击的常用方法。

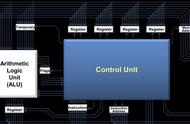

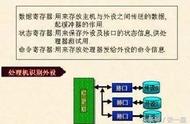

移位寄存器是执行逻辑运算或储存信息的部件,广泛存在于数字加密系统中[7]。研究表明移位寄存器是加密系统中能量消耗显著的部件之一,同时又因为它只在时钟沿到来时处理数据,相较于其他部件其工作时序变化相对固定且易于辨识,因此在差分功耗分析中常利用它的能量消耗作为破解传统密码芯片的分析点。鉴于此,本文结合SABL电路在每个时钟周期内功耗为恒定值的特征,提出一种能够防御DPA攻击的移位寄存器设计方案。首先分析静态互补CMOS电路功耗特点和SABL电路工作原理及功耗恒定特性;然后根据SABL电路特点设计清零置位D触发器,再利用SABL逻辑门和D触发器构成多位移位寄存器电路;最后在TSMC 65 nm CMOS工艺下,通过Spectre工具模拟验证所设计的移位寄存器逻辑功能的正确性和防御DPA攻击性能。

1 SABL电路

目前数字集成电路设计绝大多数采用静态互补CMOS逻辑单元实现,其总功耗由漏功耗Pleak、动态功耗Pdyn和短路功耗Pshort组成[8],如式(1)所示:

其中,Ptotal是CMOS逻辑的总功耗,Pleak是漏电流引起的功耗,Pdyn是对负载电容充放电引起的功耗,Pshort是电路导通一瞬间的短路电流引起的功耗。一般Pleak和Pshort都很小,而Pdyn对CMOS逻辑单元的功耗影响最大。由文献[8]可知,输出信号只有发生0→1跳变时,电源才对负载电容进行充电,而在0→0、1→0、1→1三种跳变情况下,电路并不会产生动态功耗。因此静态互补CMOS逻辑功耗与其所处理的数据相关,这也成为攻击者对传统密码器件展开DPA攻击的突破口。

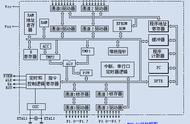

鉴于静态互补CMOS逻辑的不足,Kris Tiri于2002年首先提出具有功耗恒定特性的SABL电路[9]。它由预充管、差分网络、交叉耦合反相器、常导通管和求值管构成,其中差分网络根据其逻辑功能分为差分下拉网络(Differential Pull-Down Network,DPDN)和差分上拉网络(Differential Pull-Up Network,DPUN)。由DPDN组成的N型SABL单元电路与由DPUN组成的P型SABL单元电路结构如图1所示。

以N型SABL电路的输出信号在相邻两个时钟周期跳变情况为例,分析SABL电路的功耗恒定特性,结果如表1所示,其中,out、为电路的双轨输出信号。无论在第n个还是n 1个时钟周期,当电路进入预充阶段,双轨输出都被预充至高电平;当电路工作在求值阶段,双轨输出互补信号。分析表1数据可知,在相邻的两个时钟周期里,电路输出信号均有一次0→1跳变,即SABL电路具有恒定的信号跳变率。同时,由于差分下拉网络使得SABL电路内部所有节点都有完整的充放电过程,消除了由电荷共享导致动态功耗差异的可能性。由文献[8]知电路的功耗与其节点信号跳变率成正比,故N型SABL电路在每个时钟内能量消耗为恒定值。P型SABL电路与N型SABL电路工作过程类似,也具有功耗恒定特性,故SABL电路能够有效地防御DPA攻击。

基于SABL电路设计的两种基本逻辑门电路及符号如图2所示,利用基本逻辑门可实现具有特定逻辑功能的电路。

2 基于SABL电路的移位寄存器设计

数字加密系统中,移位寄存器是能量消耗不均衡的部件,它影响着加密系统的安全性。随着攻击技术的演化,能够防御DPA攻击的加密系统对移位寄存器的安全性提出了更高的要求。

2.1 清零置位D触发器设计

一种基于SABL电路的D触发器状态方程如式(2)、式(3)所示: