CMOS图像传感器相较于传统的CCD而言,具有更高的集成度,更灵活的图像捕获方式,更宽的动态范围,加上其低成本、低功耗的特点,越来越受到人们的重视并得到广泛的应用。但是CMOS图像传感器在采集图像过程中由于暗电流和放大器偏差等原因导致其抗噪声能力较差,引起图像噪点增多,质量下降[1],这会直接影响图像的后期处理工作。为方便图像的后续处理,在图像采集过程中,对图像进行预处理是十分必要的。

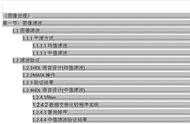

1 降噪方法

高斯噪声是数字图像中最常见的噪声[2],消除图像高斯噪声一般考虑使用均值滤波方法。传统的邻域均值滤波法对高斯噪声可以起到抑制作用[2],但是会引起图像边缘部分细节的丢失。针对图像噪声与纹理边缘的相似性,文献[2]提出一种基于置信区间的自适应加权均值滤波方法。该方法利用高斯噪声的正态分布特性,将灰度值处于置信区间内的像素点判断为噪声,能在滤除噪声的同时,保证图像边缘不受影响。但该方法需要对噪声图像的灰度均值及噪声的标准差预先进行估计,实时性较差。文献[3]提出一种基于灰度值相似度和空间邻近度的加权均值滤波算法,不仅考虑到滤波窗口中像素值的灰度值差异,也考虑到距离对中心像素点的影响,根据其两个参数局部邻域灰度因子和局部邻域空间因子,生成加权系数。该方法相比于传统的高斯滤波方法有更好的去噪效果,但运算量较大,处理速度较慢。

文献[4]设计了一种基于极值点的加权均值滤波方法。该方法可以根据图像的灰度值,自适应调整加权系数。通过4个方向上的方差计算,可以确定滤波窗口与纹理边缘是否重合,并判断出纹理的方向,据此生成不同的权重。这样就可以达到较好的去噪保边的效果。但如果使用上位机实现该算法,无法保证实时性。

通常上位机处理速度较慢,无法与图像采集、传输与存储系统形成一套流水线,而FPGA具有高速、并行、数据吞吐量大的特点,因此针对以上问题,提出一种基于FPGA实现的自适应加权均值滤波方法。该方法将文献[4]提出优化算法映射到FPGA中,实现实时的图像处理。

2 算法分析及其FPGA映射

高斯噪声是基于像素点的噪声,因此考虑使用3×3的滤波窗口[5]。采用3×3的窗口对图像进行均值滤波时,图像第1行和第1列及最后1行和最后1列的像素点会由于数据不足而无法参与运算。为保证数据的完整性,可以采用填充法[6],在处理前先对图像进行2×2的扩展。扩充后数据如图1所示,白色部分为图像原始数据,阴影部分为填充的数据。

滤波模板生成,首先需要检测窗口中心点是否为极值点,如果是则可能是噪声点或纹理边缘[7]。通过窗口4个方向上3个点方差计算确定该点是噪声还是纹理边缘,如图2所示。如果滤波窗口与纹理边缘重合,4个方向中与纹理边缘有交叉的方向,由于灰度值跳变,会出现方差较大的情况。

而与纹理边缘平行的方向上,灰度值不会出现大幅跳变,因此方差较小。根据4个方向的方差,确定纹理边缘的方向,再确定其加权系数,在穿越图像纹理边缘的方向上,不做滤波处理。方向1到4上生成加权系数分别为A、B、C、D。

A=0 0 0

以上权重的模版矩阵都符合正态分布的规律,且矩阵所有元素的和为2的整数次幂,在后续的归一化运算中,可以通过移位寄存器代替除法器实现,节省大量FPGA资源。

3 FPGA实现

本设计选用Xilinx FPGA XC6SLX45作为主控芯片,以模块化设计理念为指导,设计了分辨率可配置的加权均值滤波模块。该模块由4个部分组成,包括数据缓存模块、权重生成模块、加权求和模块以及求均值模块,四个子模块采用流水线的方式工作,保证数据能够实时处理,整体逻辑设计如图3所示。

3.1 数据缓存模块设计

数据缓存模块的功能是将1路12 bit数据流,经过缓存和时序调整调整为3路并行的12 bit数据流。该模块使用两个深度为4 K,宽度为12 bit的读优先RAM,分别用来存储一行有效图像数据。根据行同步信号Hsync和场同步信号Vsync来判断传感器采集回的数据是否有效。

每当Hsync的一个上升沿到来时,锁存输入的数据,得到每行数据的第一个像素。经过计数后,再次锁存每行数据的最后一个像素。输入的数据延时一个时钟,同时把锁存的首位数据和末位数据与输入数据组合,形成一路新的数据流,如图4所示。由于RAM_4 K用于缓存一行扩充数据,因此图像数据的宽度需要小于4 094,否则会造成数据丢失。

数据缓存模块的一个关键信号是行计数信号,当一帧图像数据到来即Vsync的一个上升沿到来时,行计数信号清零,每次Hsync的上升沿到来时,行计数加1。由于需要对数据进行扩充,因此第一行和最后一行数据做特殊处理。当第一行组合数据到来时,同时存储进两个RAM中,此时3个输出通道无输出。当第二行组合数据到来时,1通道输出第二行数据,2通道和3通道输出第一行数据,如图5所示。